Intel FPGAのSimulationの手順

Intel FPGAのSimulation

FPGAの設計は時間がかかる。

特にデバッグに時間がかかるので、コードの誤りは早い段階で検知しておきたい。

そのためにはSimulationを使いましょう。

ここではIntel FPGAのModelsim-Alteraの使い方を簡単にまとめる。

流れ

- プロジェクトの作成

- verilog fileの作成

- テストベンチのテンプレートの作成

- テストベンチの作成

- Modelsimの起動とSimulationの実行

プロジェクトの作成

Quartus PrimeのFile > New Project Wizardをクリック

適当に進めてProjectを作成する

この画面でModelsim-alteraを選択する

verilog fileの作成

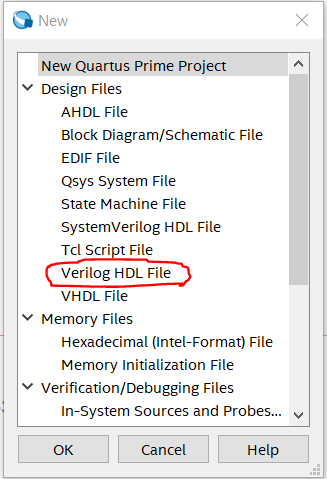

- Quartus PrimeのFile > Newをクリック

Design Files > Verilog HDL Fileをクリック

Verilogで書く。

- Start Analysys & Synthesisをクリックし、エラーが出ないことを確認する。

テストベンチのテンプレート作成

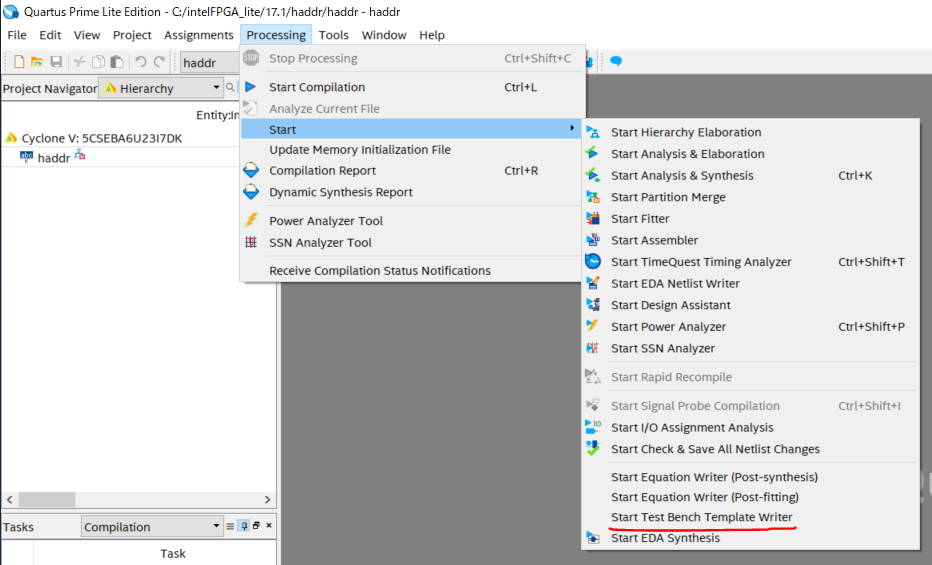

Quartus PrimeのProcessing > Start > Start Test Bench Template Writerをクリックする。

プロジェクトフォルダ/simulation/modelsimフォルダ内に、"モジュール名".vtのファイルが生成される。

これがテストベンチのテンプレート。

入出力と内部信号が記載されている。便利。

テストベンチの作成

生成されたテストベンチテンプレートファイルを編集する。

ご丁寧にinitialとalwaysまで記載されているので、そこにinput信号の記載。プロジェクトを右クリックしてSettinsを選択。

EDA Tool SettingsのSimulationを選択。

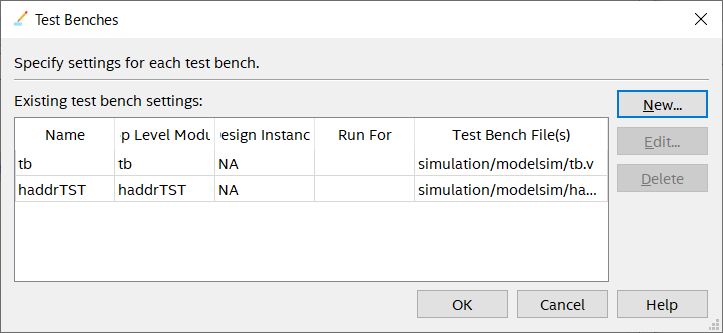

NativeLink settingsのCompile test benchをチェックし。Test Benchesをクリック。

Newをクリック。

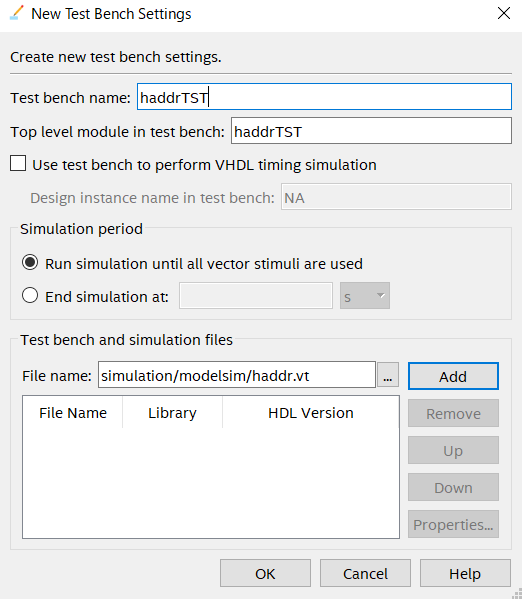

テストベンチ名を適当に入力し、Test bench and simulation filesのFile nameに作成したテストベンチを選択して入力してOKをクリック。

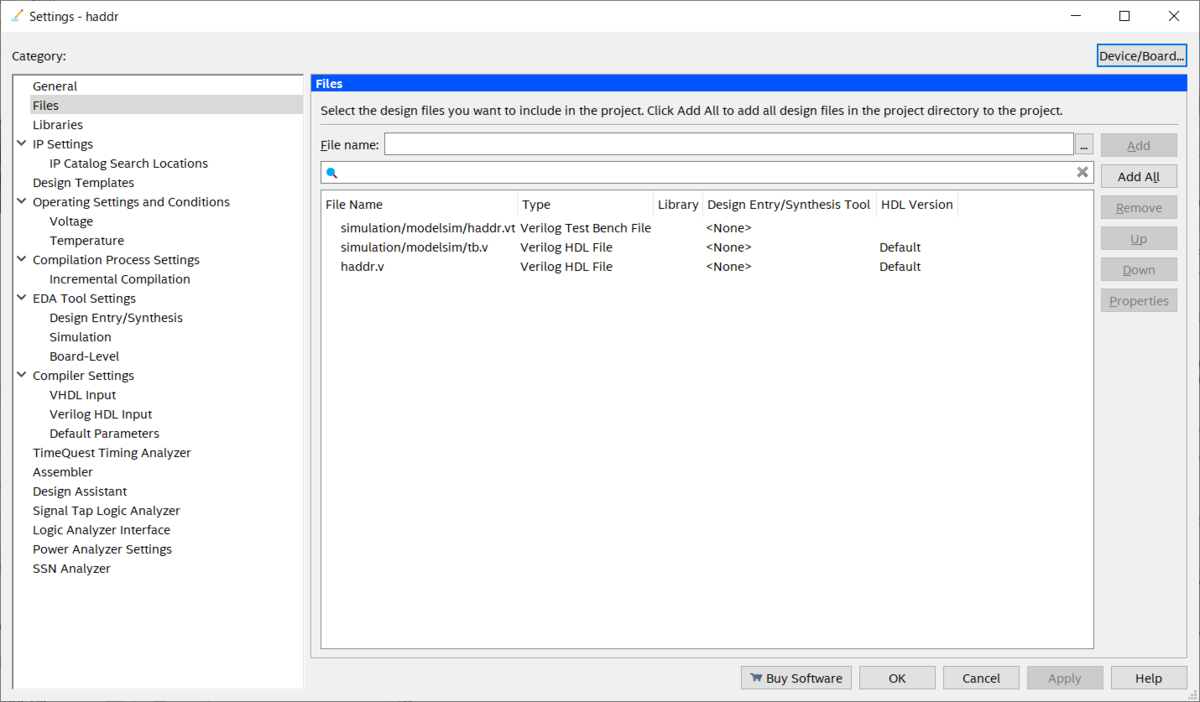

再びプロジェクトを右クリックしてSettingsを選択し、以下の画面のFilesをクリック。File名に先ほど作成したテストベンチを選択して追加する。

Modelsimの起動とSimulationの実行

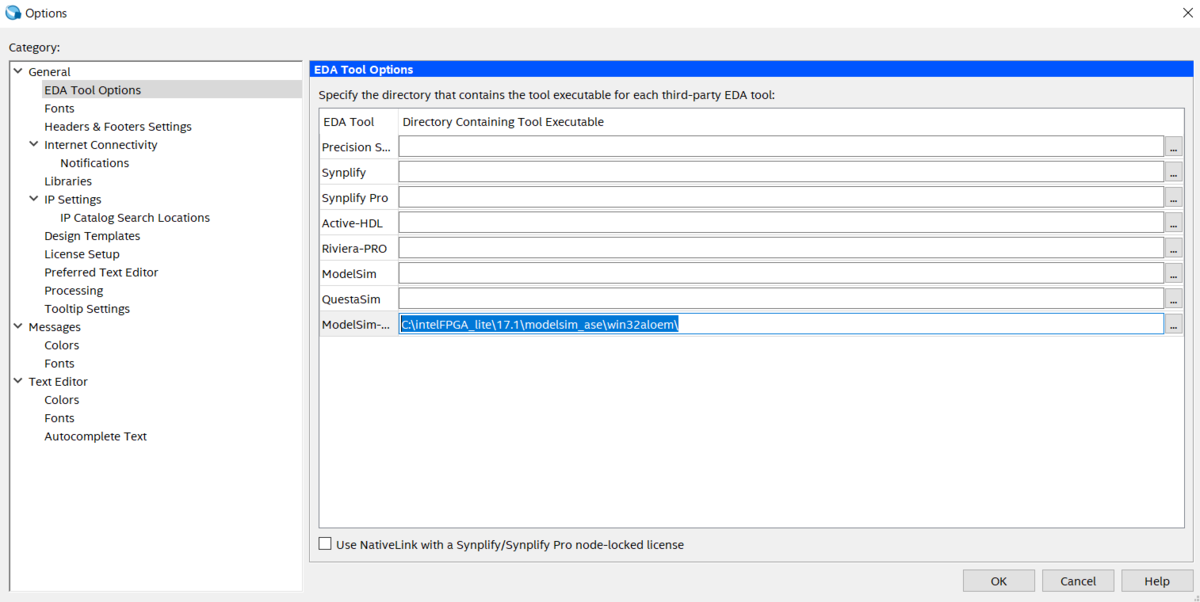

ModelSimのPathを設定するため、Quartsu Primeの Tools > Optionをクリック。

GeneralのEDA Tool OptionsのMdelSim-AlteraにPathを選択して記入する。

自分の場合は"C:\intelFPGA_lite\17.1\modelsim_ase\win32aloem\"

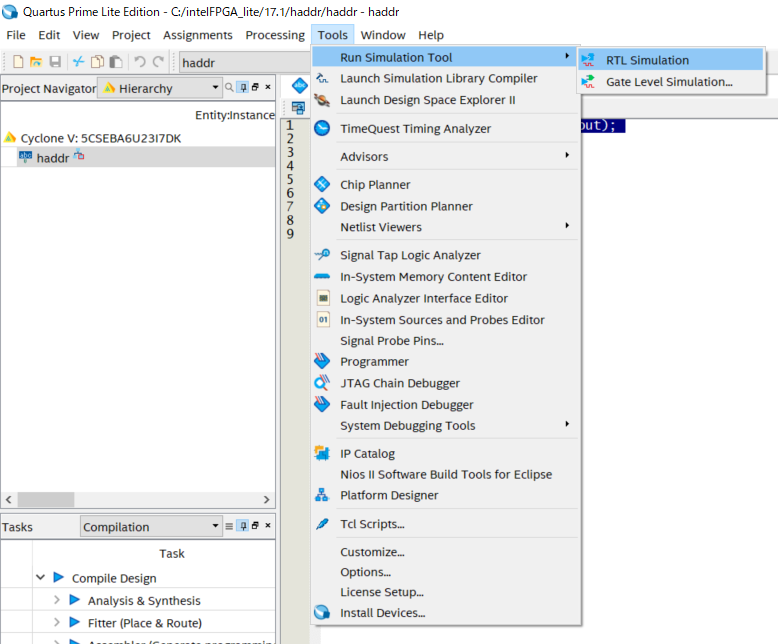

Modelsim-alteraを起動するため、Quartus Primeの Tools > Run Simulation Tool > RTL Simulationをクリック。

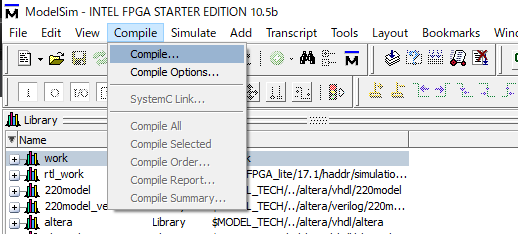

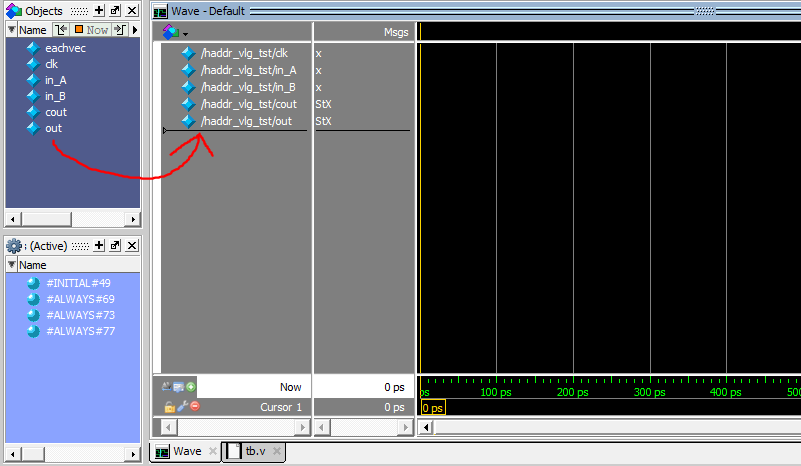

workの中にテストベンチがある事を確認する。

記述に誤りがありコンパイルができず表示されない。

その場合はテストベンチを修正し、Compile > Complieをクリックし、テストベンチをコンパイルする。

Simulationを実行するため作成したテストベンチのファイル名をダブルクリックする。

Waveタブをクリックし波形を表示する。

閲覧したいネットをドラッグしWaveにドロップする(まだ波形は表示されない)。

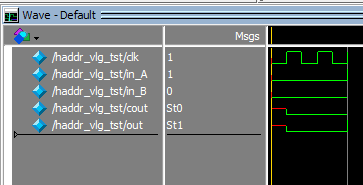

閲覧したい波形の最大時間を設定し、Runボタンをクリックする。

波形が表示される。

まとめ

手順が多いので地味に大変。基本は以下の3つ。

- テストベンチファイルを記述

- テストベンチの作成

- プロジェクトにテストベンチファイルを追加

2と3のいずれかをうっかり忘れてしまいがちなので

上手くいかない場合は、2か3をやり忘れていないか要確認。